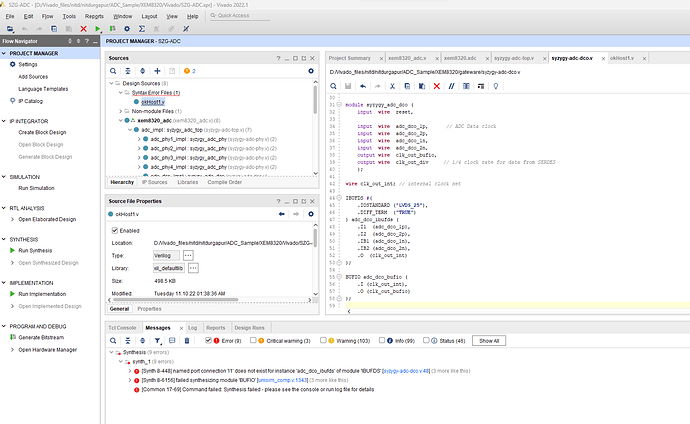

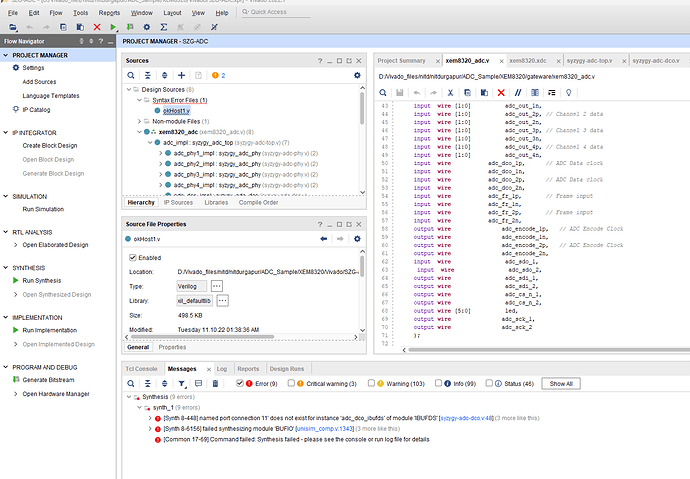

Constraint_PORTA+PORTB.pdf (73.2 KB)

We are trying to acquire real time signal through syzygy ports (A,B,C,D). Due to IO problems, we are not able to make PORT-C and D work. Hence, we’re trying to operate PORT A and B at a time (all the 4 channels active). We have changed the .xdc file(where PORTA and PORTB pins are defined) and changed signal names in the respective modules of the reference design. Screenshots are attached in this thread. What are the modifications must be done on the reference design to make the syzygy PORT A and B work simultaneously?